Reverse Engineer and create Data flow

by looking at first picture we can create second picture's right , which is data flow graph.

and by looking at data flow graph we can create left instructions.

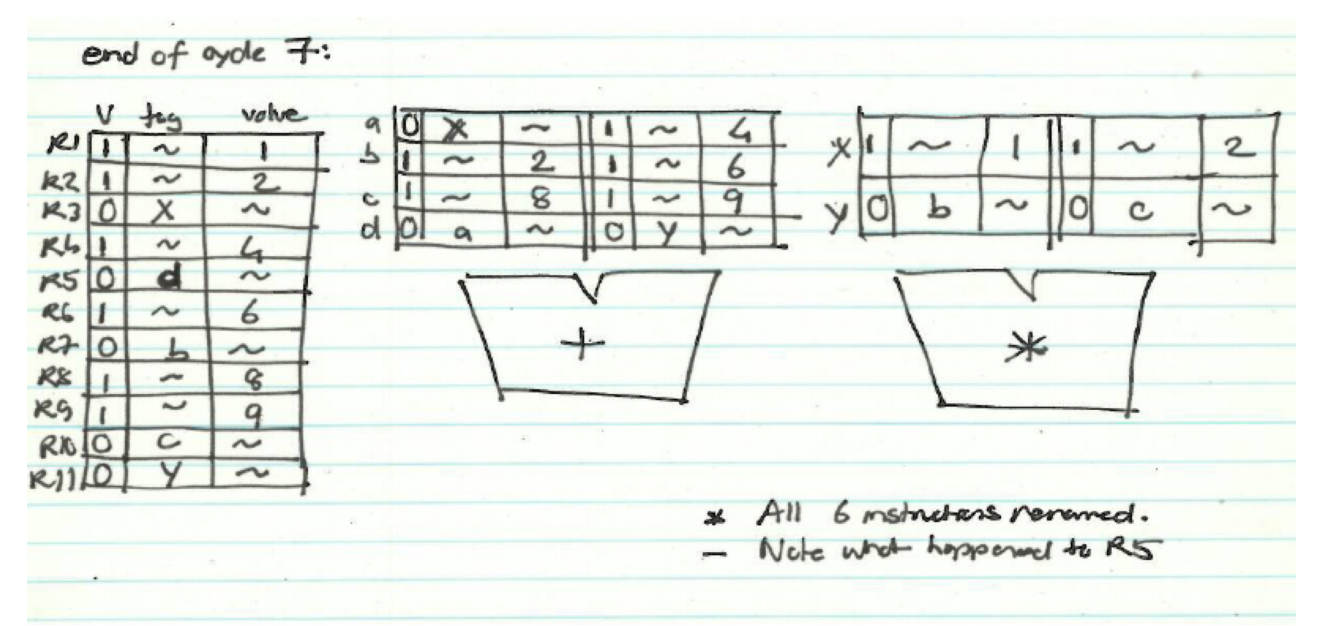

Out of Order Execution with Precise Exception

user reorder buffer to reorder instructions before committing them to architectural state

instruction updates the Register alias table(RAT, frontend register file) when it completes exectuion

instruction updates a seperate architectural register file when it retires , in other words the architectural register file is always updated in program order

exception = flush pipeline , copy archietectural register file into frontend regsiter file

using PRF (pyhsical register file) we don't have to broadcast value we just need some pointer.

Frontend Register File are used for renaming , Architectural register file is just pointing to PRF if instruction become oldest after finsh.

if both Frontend RF and Architectural RF points to same PRF . This means that no instruction is writing the result to this register.

There are complicated issue with load and store

Content addressable search = based on load address

Range search = based on address and size of both the load and earlier stores

Age based search = search with last written values

load data can come from a combination o fmutiple places = one or more stores in the store buffer (SQ)

'Computer Architecture > C.A (ETH Zürich, Spring 2020)' 카테고리의 다른 글

| Lecture 18a: VLIW (0) | 2021.07.11 |

|---|---|

| Lecture 16: Branch Prediction (0) | 2021.07.10 |

| Lecture 15a: Out-of-Order Execution (0) | 2021.07.07 |

| Lecture 14: Pipelining Issues (0) | 2021.07.05 |

| Lecture 13: Pipelining (0) | 2021.06.28 |