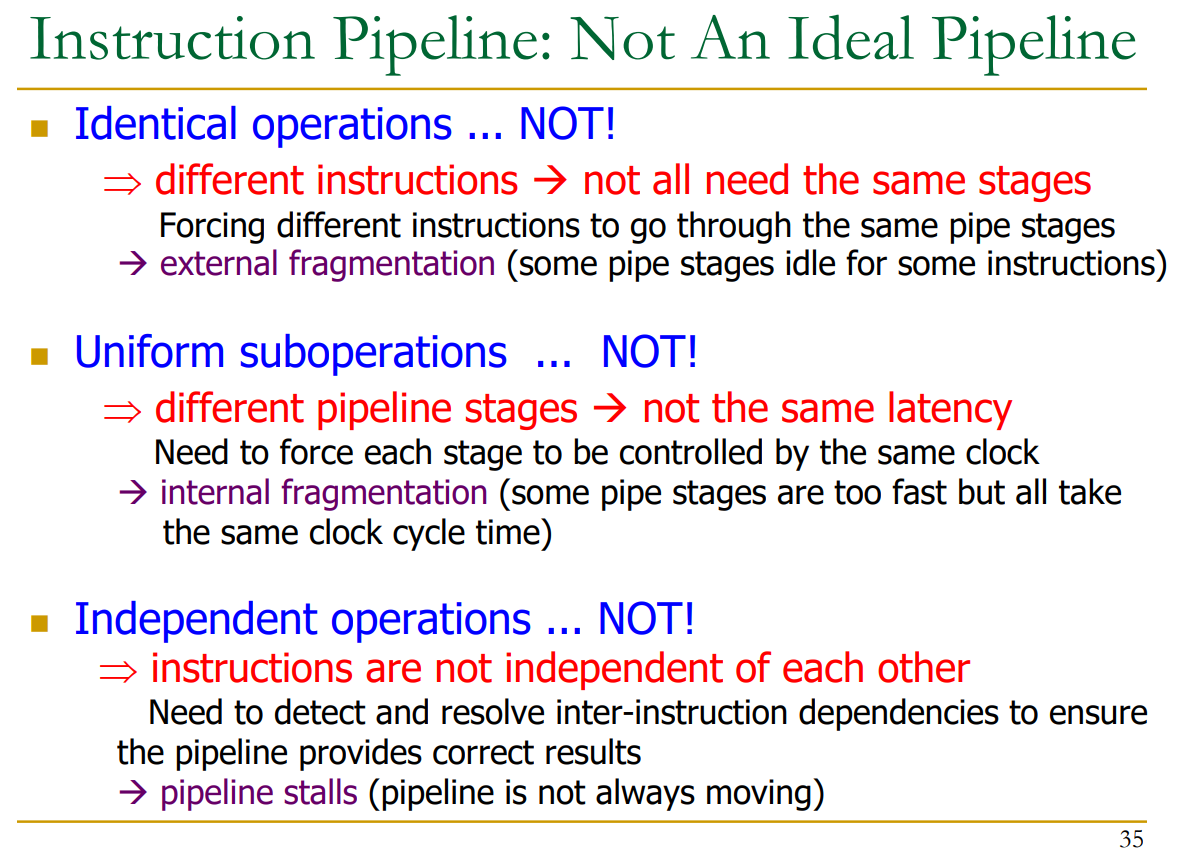

the time might not be equal and something might take longer.

just buy another dryer (hardware) and we can increase output.

actutal time takes longer than T/k , at we are not just summing one latch dealy

if pipe line is 20 stage pipelined version we need to add 20 * latch delay.

which cause individual instruction execution time will be increase but hopefully overall throughput will increase.

there is always trade off between latency and throughput.

stall = not always moving meaning

- Resource contention

- Dependences , between instructions (Data, control)

- Long latency (muti cycle) operations

Resource contention (possible solution)

- eleminate the cause of contention = duplicate the resource or increase its throughput.

- detect the resource contention and stall one of the contending stages , but not very good idea , stalled resource might be used often.

Data Dependences

- Flow dependence (true data dependence - read after write)

- Output dependence (write after write)

- Anti dependence (write after read)

flow depenedences always need to be obeyed because they are constitute true dependence on a value

anti and output dependences exist due to limited nubmer of architectural registers.

notice flow dependence will still happen eventhough there are more registers. but others wont' happen.

Software dectection

if there are dependency in insturctinos compiler find independent instruction and fill them, and put them between dependent insturctions so we can have full pipeline.

there are always NOP which are implemented to fill pipeline if compiler can't find one.

but compiler must make sure it does't break program. cause order might matter in some program.

Cominational dependence check logic

checking dependecy using combinational logic.

if one of src register equals rx,ry,rz then we make stall the instruction because there is dependency.

'Computer Architecture > C.A (ETH Zürich, Spring 2020)' 카테고리의 다른 글

| Lecture 15a: Out-of-Order Execution (0) | 2021.07.07 |

|---|---|

| Lecture 14: Pipelining Issues (0) | 2021.07.05 |

| Lecture 12: Microarchitecture II (0) | 2021.06.22 |

| Lecture 11: Microarchitecture I (0) | 2021.06.17 |

| Lecture 10a: Instruction Set Architecture (0) | 2021.06.14 |