Lecture 8: Timing & Verification

Delay is happens due to capacitance and resistance in a circuit.

- Rising and falling (1 -> 0) iuts

- different inputs have different delays

- changes in environment

- Aging of the circuit

Contamination delay (tcd) = delay until Y starts changing , minimum possible delay

Propagation delay (tpd) = delay until Y finishes changing , maximum possible delay

need to wait until value get settle.

even same gate might have different delay due to manufacturer.

Glitches

one input transition causes mutiple output transitions

notice when input changes to 1 to 0. the fast path will have an impact first.

glitch might be not desirable because something might happen in zero term which you might don't want.

by adding A`C , now there are no trasition among prime implicants , it works as a bridge.

but fixing might be undesirable it has cost. (chip area, power consumption)

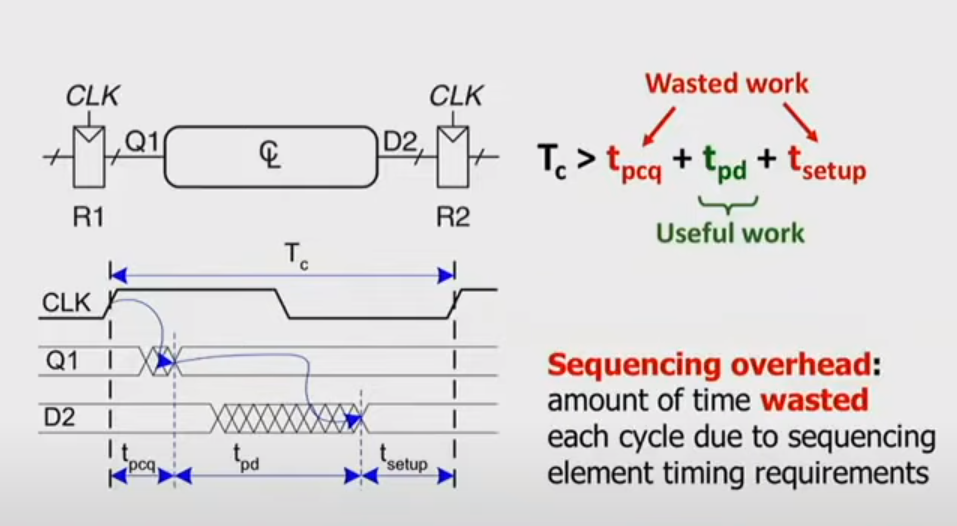

setup time = time before the clock edge that data must be stable

hold time = time after the clock edge that data must be stable.

if D is changing when sampeld , metastablilty can occur like above.

time pcq (Propgation delay clock to q) = latest time after the clock edge that Q stops changing.

time pd = doing combinational logic

time set up = settling the combinational logic output.

it is reason whay CPU HZ isn't too high. more frequency will cause more waste of time.

These conditions must be satisfied in order not to lead to a metastablilty phenomenon.

you cannot solve this problem by changing the clock cycle time.

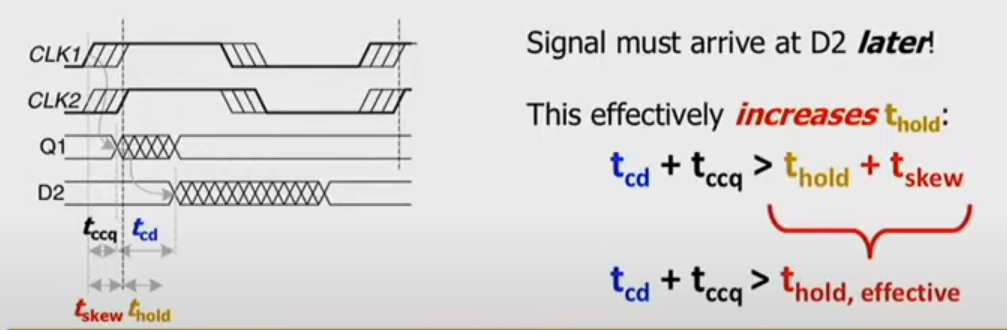

Clock skew

the clock doesn't reach all parts of the chip at the same time.

due to clock skew when considering clock cycle we need to add clock skew time into account.

time skew = it is assuming worst-case ( clock arrives R2 first )

eventually the total hold time need to be increased.

designer use 'clock network' to ensure clock arrives all the locations at the same time.